Small Simple FPGA 16-bit Microprocessor (SSFP16)

Hintergrund und Zweck

Die Entwicklung war eine reine Übung, ohne praktische Anwendung. Gerade deswegen kann sie auch für andere interessant sein.

Merkmale und Architektur

- Harvard-Architektur mit 16-bit Datenbus und 16-bit Steuerbus.

- Alle Befehle sind 16 bit breit. Ein Befehl enthält bis zu 3 Operanden.

- Addressierungsarten: Unmittelbar, direkt, indirekt und indirekt mit Basis.

- Alle Operationen beziehen sich auf 16-Bit Werte, nur Schreiben in RAM ist auch mit 8-Bit Breite möglich.

- Befehle zum Lesen/Schreiben von externem Daten-RAM oder Daten-ROM.

- Divisionsbefehle.

- Separate I/O-Befehle.

- Interrupt-Eingang.

- Parity-Prüfung für Daten und Befehle.

- Maximaler Prozessortakt mit Spartan 3, Geschwindigkeitscode -4: 66 MHz.

- Alle Befehle benötigen 1 Takt, mit Ausnahme von Laden aus dem Speicher (2 Takte) und den Divisionsbefehlen (17 Takte).

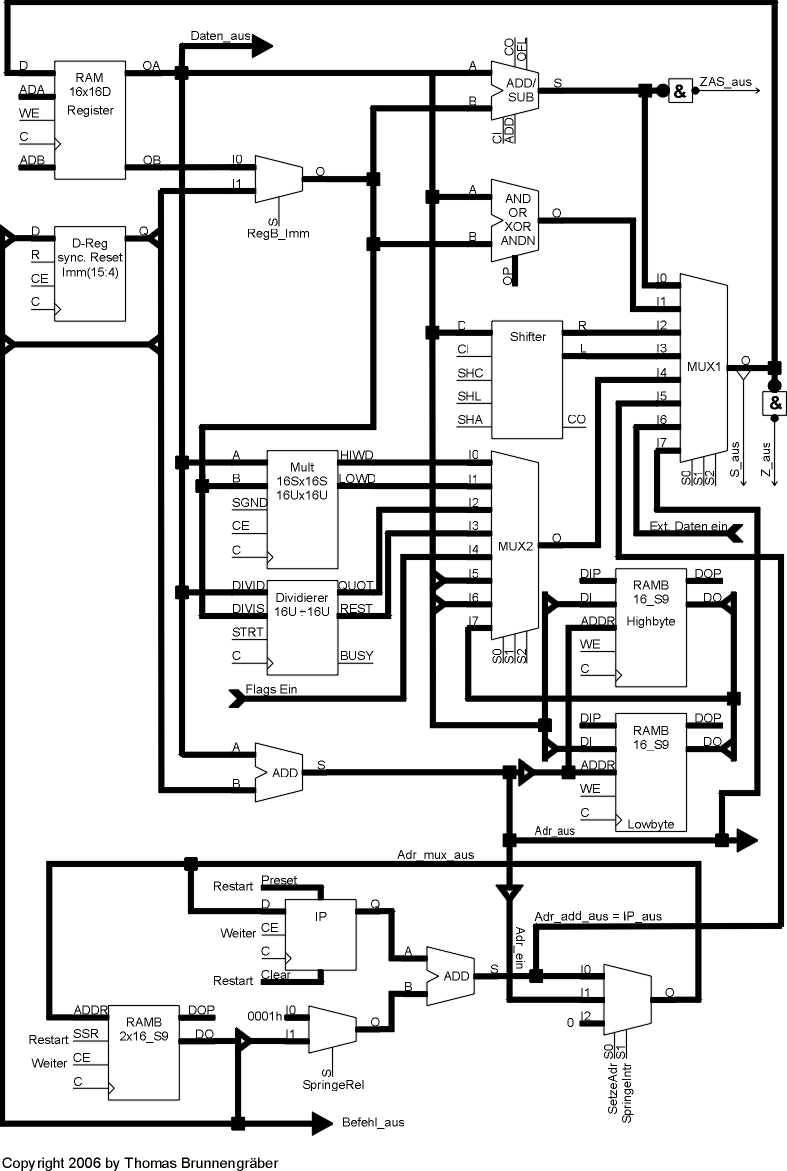

Strukturbild

Bild 1: SSFP16 Struktur

Sprache, Dokumentation und Tools

Prozessor

Die Beschreibung des Prozessors erfolgte in VHDL und ist für Spartan 3 optimiert. Die Synthese erfolgte mit ISE Webpack 8.1. Soweit möglich wurde das Verhalten beschrieben. An einigen Stellen hat ISE WebPack 8.1 mit der Verhaltensbeschreibung nicht das optimale Ergebnis gefunden, dort wurden daher Strukturbeschreibungen verwendet.

Der Prozessor ist ausführlich in deutscher Sprache in HTML-Format dokumentiert. Die Dokumentation ist Teil des Downloads und unterliegt der GNU Free Document License.

Assembler

Will man nicht Befehle von Hand codieren, muss ein Assembler her. Da ich auf die Schnelle nichts Brauchbares gefunden habe (entweder ohne jegliche Dokumentation oder zu einfach oder zu kompliziert), habe ich einen relativ einfacher Kommandozeilen-Assembler in C geschrieben. Er sollte mit jedem C-Compiler auf vielen Plattformen zu kompilieren sein. Ich nutzte sowohl gcc unter Linux als auch Dev-C++ mit mingw32.

Für Microsoft Windows ist der Assembler als Binär-Datei ssfp16asm.exe im Download enthalten.

Bei Aufruf von ssfp16asm ohne Parameter wird eine Befehls-Referenz angezeigt.

Die Beschreibung des Assemblers ist Teil der HTML-Dokumentation.

Simulator und Debugger

Da sich in einem FPGA relativ schwer Fehler suchen lassen, schrieb ich einen Simulator in Java, welcher gleichzeitig als Debugger dient. Der Prozessor wurde dabei nahezu auf RTL-Ebene abgebildet, was die Suche von Fehlern im VHDL-Code vereinfacht, aber natürlich für das Debuggen von Assembler-Programmen unnötig langsam ist.

Die Beschreibung des Simulators/Debuggers ist Teil der HTML-Dokumentation.

Letztlich benötigt habe ich ihn dann doch nur für das Debuggen von Assembler-Programmen, da im VHDL-Code von Anfang an wider Erwarten keine wesentlichen Fehler waren. Da das Lernziel damit erreicht war, erfuhr der Debugger keine Erweiterung des Funktionsumfangs. Auch die Implementierung ist sicher kein Muster für gute oder gar effiziente JAVA-Programmierung.

Rechtliches

Sämtliche Quellcodes dieses Projekts unterliegen der GNU General Public License. Dies trifft auch für die VHDL-Beschreibung des Prozessors zu, welche ebenfalls zu Software im Sinne der GNU GPL gerechnet wird. Ich behalte mir vor, die von mir erstellten Teile zu einem späteren Zeitpunkt auch unter andere Lizenzen zu stellen. Dies gilt selbstverständlich nicht für ggf. zukünftig von Dritten gemäß GNU GPL entwickelte Module oder Verbesserungen.

Dieses Projekt ist in erster Linie zu Demonstrations- und Lehrzwecken gedacht. Eine patentrechtliche Prüfung konnte daher nicht vorgenommen werden. Da ich jedoch keinerlei Vorlagen für dieses Projekt nutzte und trotz meiner nur unwesentlich über Studieninhalte hinausgehenden Kenntnisse bezüglich Mikroprozessor-Architektur an keinem Punkt mehr als wenige Stunden nachdenken musste, gehe ich davon aus, zumindest kein Patent verletzt zu haben, welches diese Bezeichnung verdient.

Schließlich möchte ich noch darauf hinweisen, dass keinerlei Gewährleistung für die hier veröffentlichten Quelltexte besteht, da diese kostenlos lizensiert werden. Der hier veröffentlichte Quelltext steht so zur Verfügung, “wie er ist”, ohne irgendeine Gewährleistung, weder ausdrücklich noch implizit, einschließlich aber nicht begrenzt auf Marktreife oder Verwendbarkeit für einen bestimmten Zweck. Das volle Risiko bezüglich Qualität und Leistungsfähigkeit der Programme bzw. des vorgestellten Mikroprozessors liegt bei Ihnen. Sollte sich eines der Programme oder der Mikroprozessor als fehlerhaft herausstellen, liegen die Kosten für notwendigen Service, Reparatur oder Korrektur bei Ihnen. In keinem Fall ist irgendein Copyright-Inhaber oder irgendein Dritter, der diese Programme oder die Hardware-Beschreibungen gemäß der GNU GPL modifiziert oder verbreitet hat, Ihnen gegenüber für irgendwelche Schäden haftbar, einschließlich jeglicher allgemeiner oder spezieller Schäden, Schäden durch Seiteneffekte oder Folgeschäden, die aus der Benutzung der Programme oder der Hardware-Beschreibungen oder der Unbenutzbarkeit derselben folgen (einschließlich aber nicht beschränkt auf Datenverluste, fehlerhafte Verarbeitung von Daten, Verluste, die von Ihnen oder anderen getragen werden müssen, oder dem Unvermögen des Programms, mit irgendeinem anderen Programm zusammenzuarbeiten), selbst wenn ein Copyright-Inhaber oder Dritter über die Möglichkeit solcher Schäden unterrichtet worden war.

Download

Der Download enthält:

- Alle für die Synthese des Prozessors mit ISE WebPack 8.1 nötigen Dateien.

- Die Dokumentation des Prozessors, Assemblers und Simulators in HTML (Befehlsreferenz als PDF).

- Den Assembler als Quellcode und Binärdatei für Microsoft Windows.

- Den Debugger/Simulator als Java-Quellcode und Klassendateien.

- Testdateien